728x90

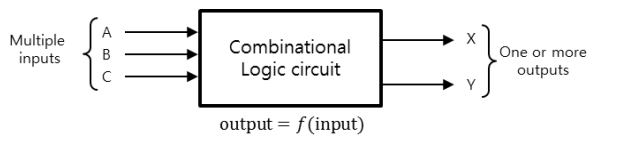

Combinatorial Logic Circuit 조합 논리 회로

- 현재 입력으로만 출력이 나오는 디지털 로직이다.

- 산술논리장치(ALU) , half adders, full adders, multiplexers, encoders, and decoders 등이 있다.

- half adders : 올림 자릿수를 처리하지 못하고 입력이 2개뿐인 가산기

- full adders : 올림 자릿수까지 한번에 사용하는 가산기

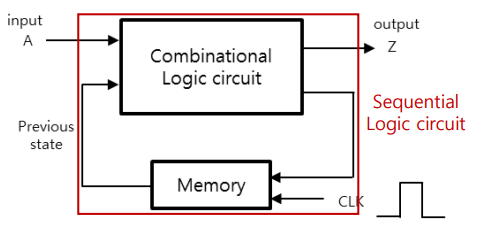

Sequential Logic Circuit 순차 논리 회로

- 현재 입력과 과거의 입력을 이용해서 출력이 나오는 디지털 로직이다.

- sequential logic circuit(순차 논리)은 상태(메모리)를 가진다는 점

- 조합논리에서는 상태(메모리)가 없다.

- 예시 : TV채널 / 볼륨 변경하기

조합 논리 회로를 설계하는 방법론

- How to design combinatorial logic circuits?

- Two-level Canonical Forms (2단계 정식 양식)

- Programmable Logic Devices (프로그래머블 논리 소자)

- Karnaugh Map (카르노 맵)

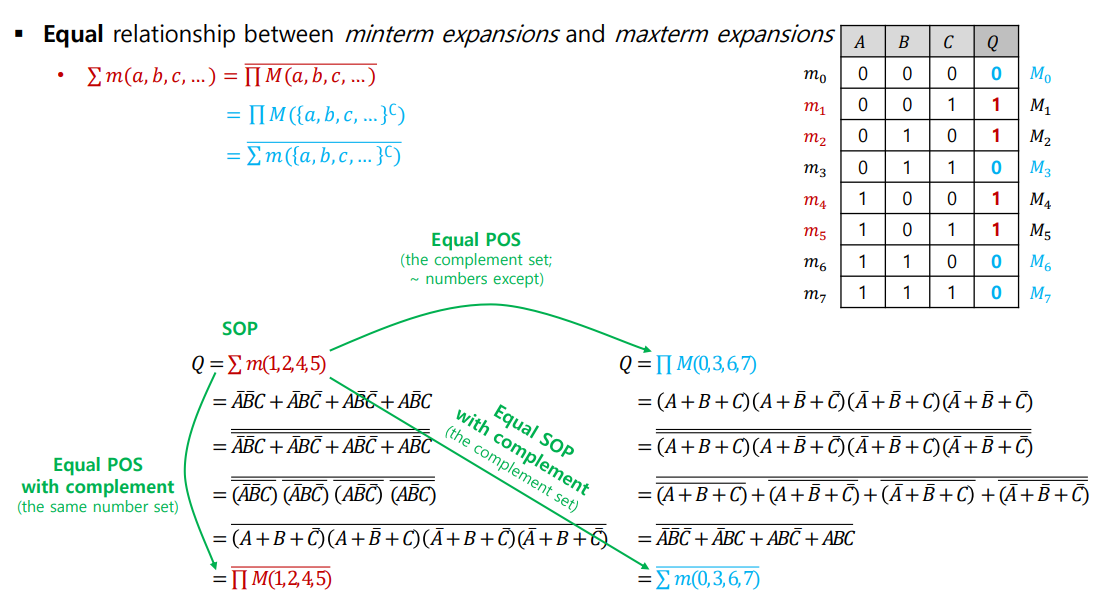

Two-level canonical forms

- 모든 조합 논리는 Two-level canonical forms을 이용해서 표현할 수 있다.

- 합의 곱 형식, 곱의 합 형식이 있다.

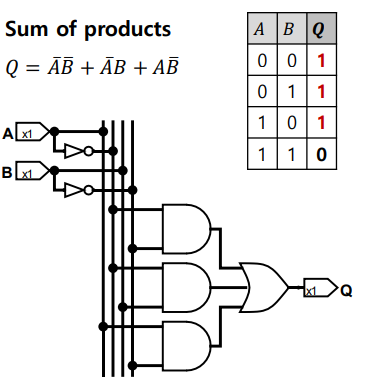

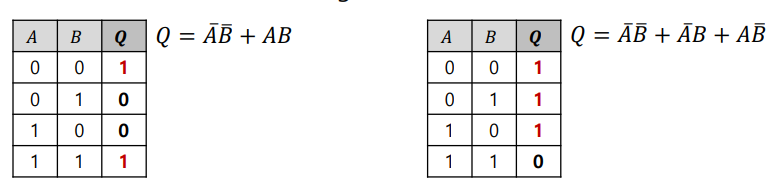

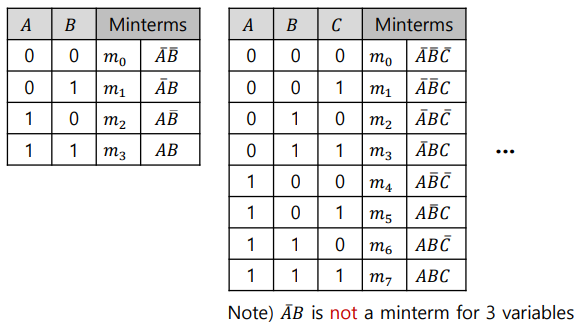

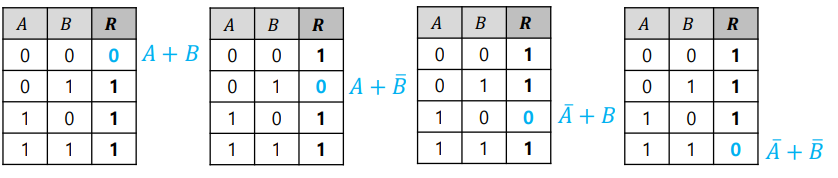

1. Sum of products(곱의 합 형식)

예시

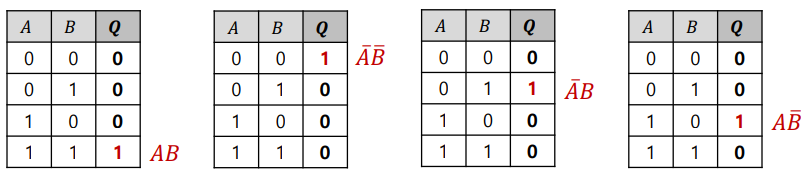

곱의 불린 표현법

곱의 합 예시

특징

- 합의 곱 형식은 SOP라고 불린다.

- 정규분리 형식 또는 최소 확장 이라고 불린다.

- SOP는 2단계 로직이다.

1단계 : 모든 입력 또는 그들의 보수를 곱한다.

2단계 : 그것들을 합한다.

예시

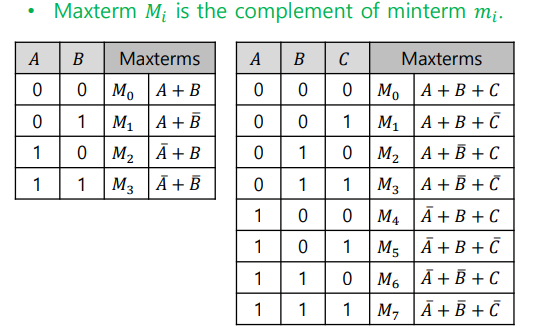

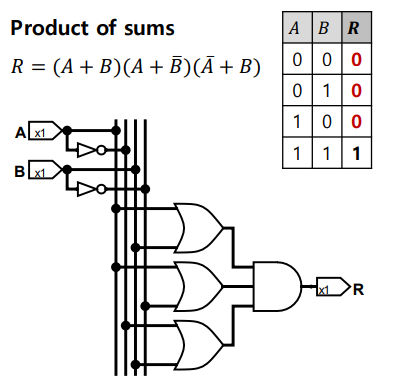

2. Product of sums (합의 곱 형식)

예시

부울방정식 합

보수 표현 예시

특징

- 합계의 곱 (POS)

예시

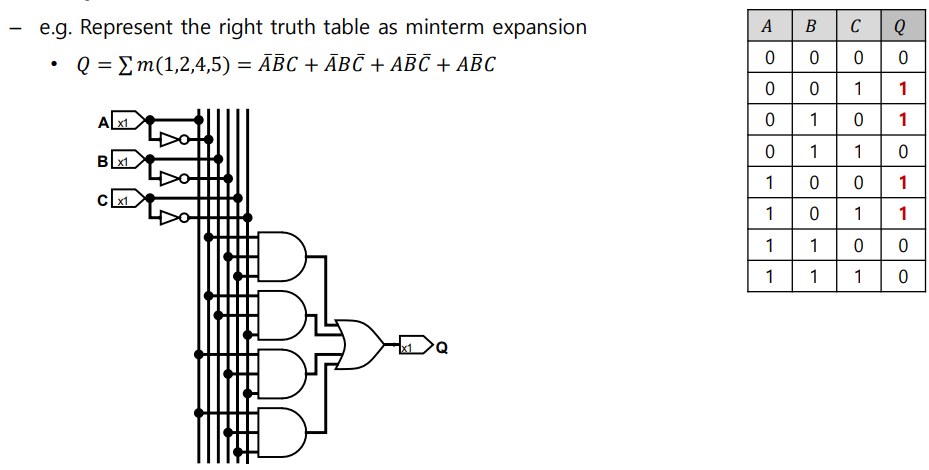

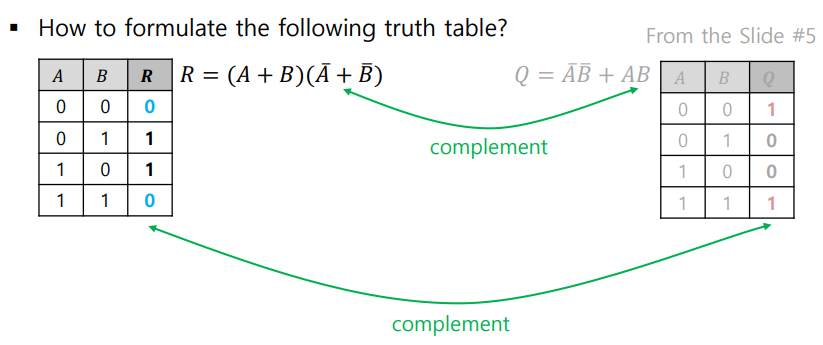

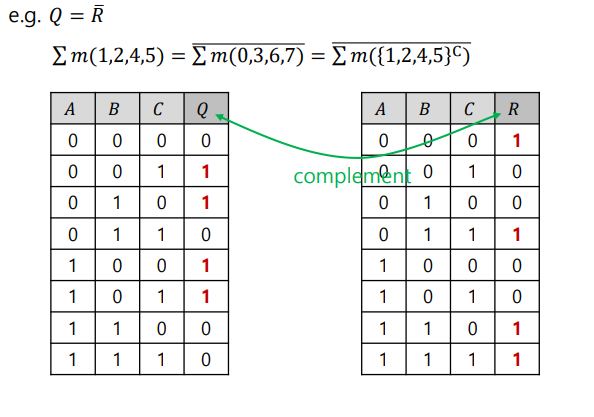

Minterm과 Maxterm사이에는 보수관계가 존재한다.

𝑚𝑖 and 𝑀𝑖 are complement each other.

- e.g. The truth table of 𝑚𝑖 is 1, 0, 0, 0, …

- e.g. The truth table of 𝑀𝑖 is 0, 1, 1, 1, …

보수관계 식

진리표

minterm과 maxterm 간의 보수 예시

minterm 간 보수관계 예시

확장관계 정리 그림

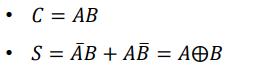

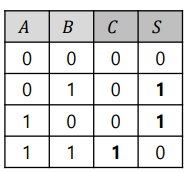

Half adder 디자인

1-bit binary digits 두자리를 추가한다.

- input은 A와 B이고

- output 은 sum(S)과 carry(C)이다.

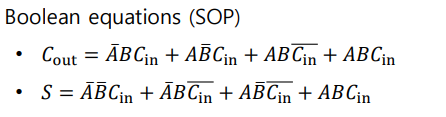

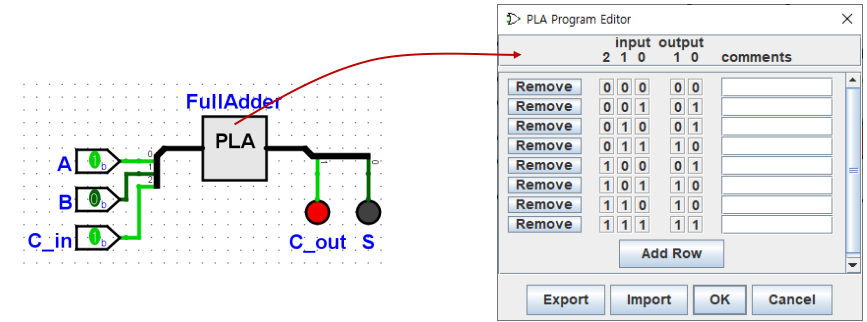

Full adder 디자인

Programmable Logic Devices

- Programmable logic device (PLD)

- 재구성 가능한 디지털 회로에 사용되는 전자 부품이다.

- e.g. PROM (in the early age), PLA, PAL, FPGA, …

Programmable ROM (PROM)

- ROM을 lookup table로 사용한다.(input: memory address, output: memory content) – e.g. Full adder implementation using ROM

lookup table(혼자 찾아본거)

Lookup table은 일련의 입력 값과 각 입력 값에 대응하는 출력 값을 가지고 있으며, 입력 값을 검색하여 해당하는 출력 값을 찾아낼 수 있습니다. 예를 들어, 8비트 이진수의 모든 조합에 대해 미리 계산된 결과 값을 저장하는 Lookup table을 사용하여 이진수 연산을 수행할 수 있습니다.

Lookup table은 검색과 변환 작업을 빠르고 쉽게 수행할 수 있으며, 큰 양의 데이터를 처리하는 데 유용합니다. 하지만, 메모리 공간을 많이 차지하고, 모든 가능한 입력 값에 대한 출력 값을 미리 계산해야 하기 때문에, 저장 공간이 큰 문제와 미리 계산해야 할 출력 값이 많은 문제가 있습니다.

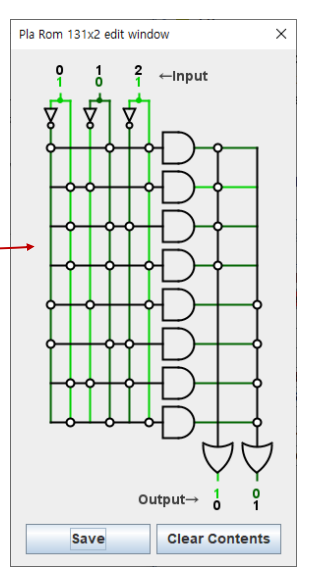

Programmable logic array (PLA)

AND게이트 플레인과 OR게이트 플레인 세트가 있는 프로그래밍 가능 논리 소자이다.

PAL 및 GAL에는 프로그래밍 가능한 AND게이트 평면이 있지만 고정된 OR 게이토ㅡ 평면도 같이 있다. → 재구성 가능성은 낮지만 빠르고 저렴하다.

제품 합산(SOP) 양식을 직접 구현할 수 있다.

예시 그림

직접 구현하기 예시

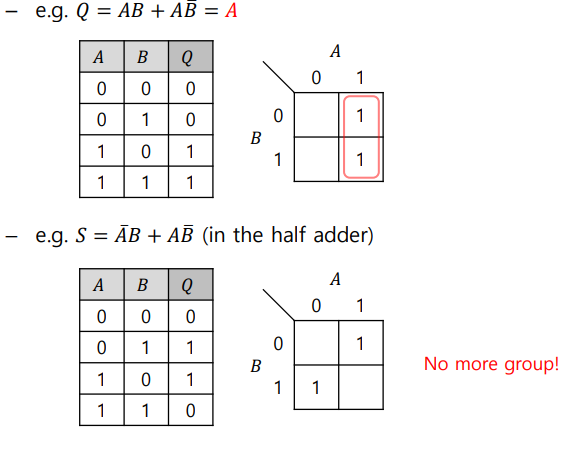

카르노 맵 (K-map)

- 주어진 진리 테이블에서 단순화된 부울 방정식을 도출하는 체계적인 방법이다.

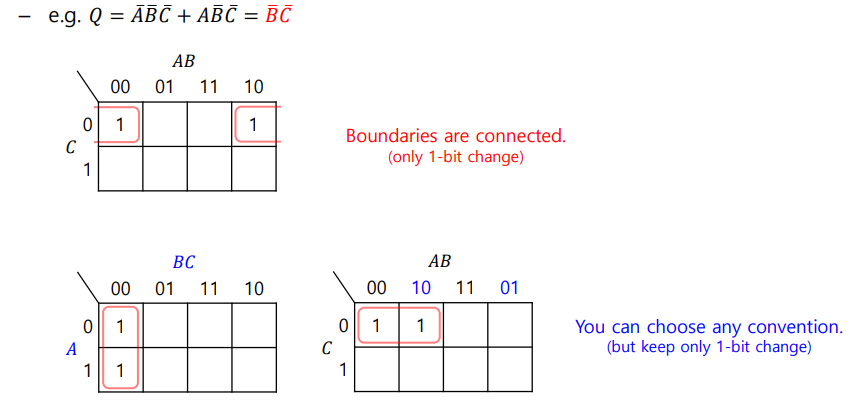

- K-map은 1비트만을 변화시켜서 표시할 수 있다.

- 변수가 6개 이상인 부울 방정식은 k-MAP으로 표현할 수 없다.

- 2-4변수 : 2D kmap, 5-6 변수 : 3D k-map(난이도 높음)

K-맵 설계 절차

1. 주어진 진리 테이블을 인접한 요소가 1비트 변화(~ 회색 코드)를 갖는 K-맵으로 표현합니다.

- SOP 양식의 경우 1(1로 표시)과 관심 없음(X로 표시)에만 체크합니다.

2. 너비와 높이가 짝수(또는 1)인 가장 크게 연결된 직사각형 그룹을 찾습니다.

3. 가장 큰 직사각형 그룹을 단순화된 부울 방정식으로 작성합니다.

변수 2개 예시

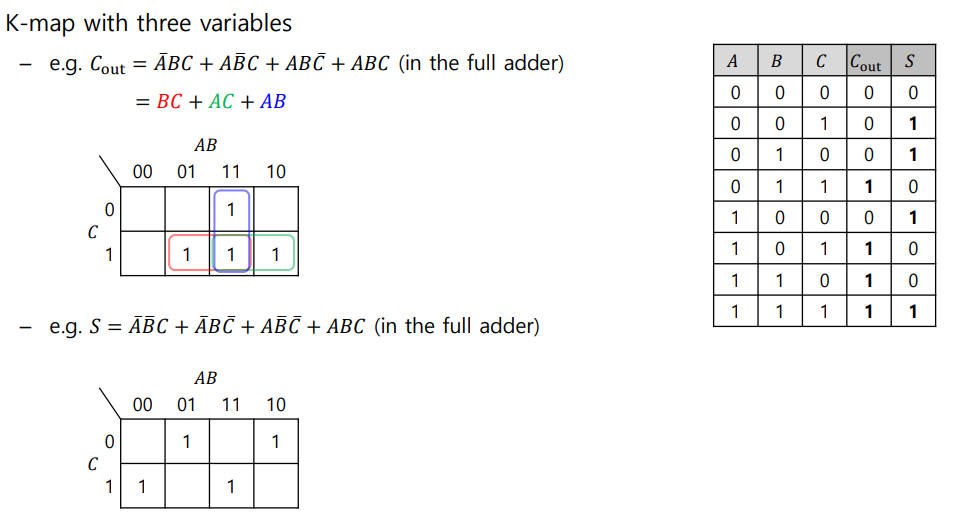

변수 3개 예시

- 예시 1

- 예시2

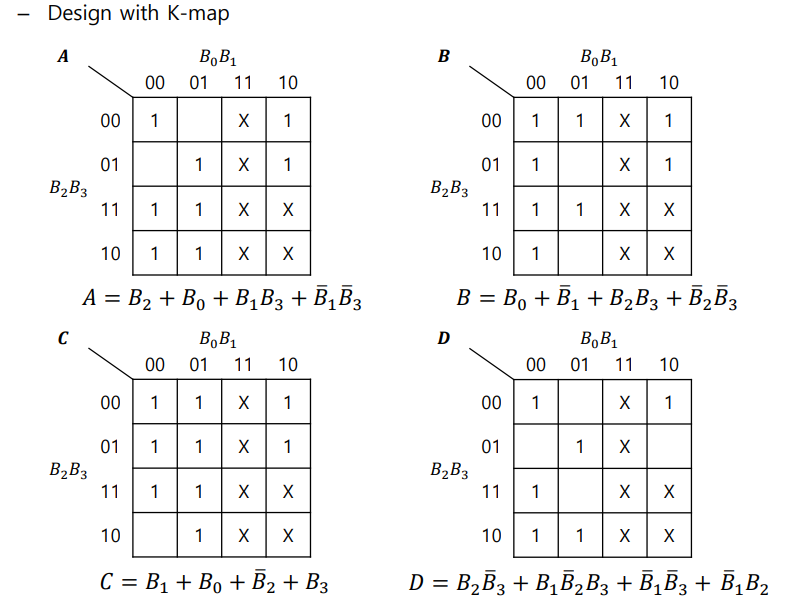

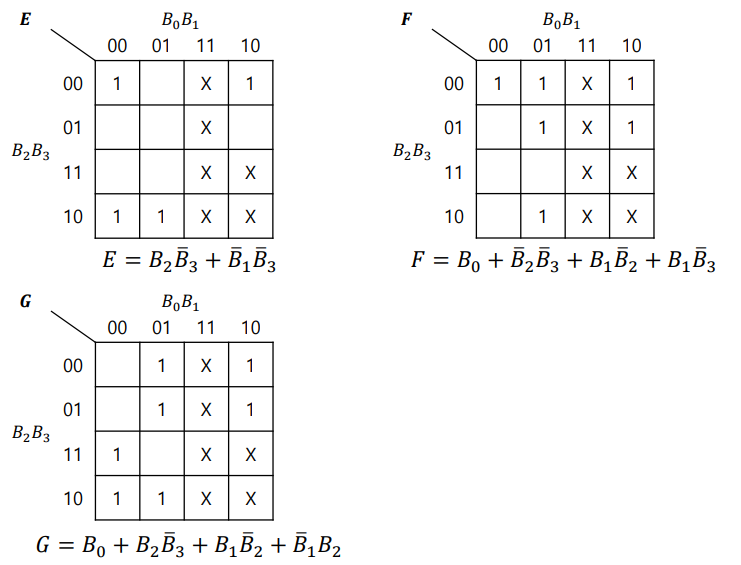

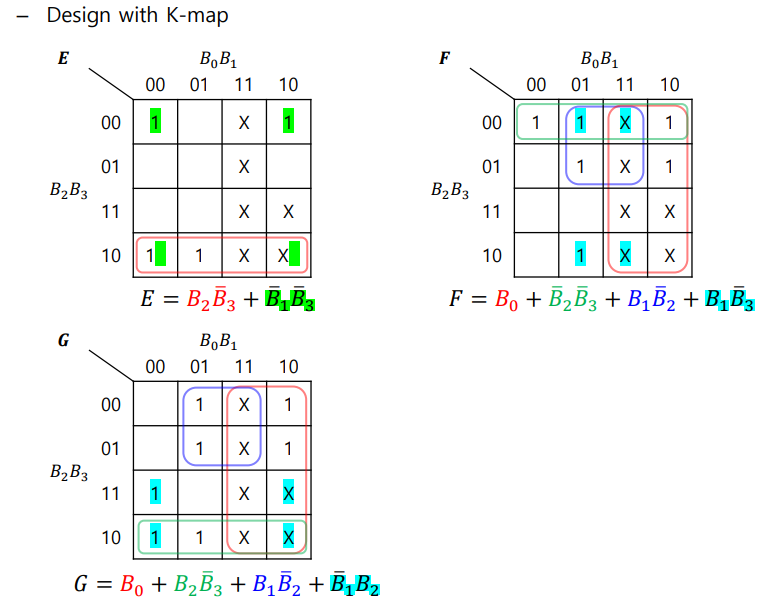

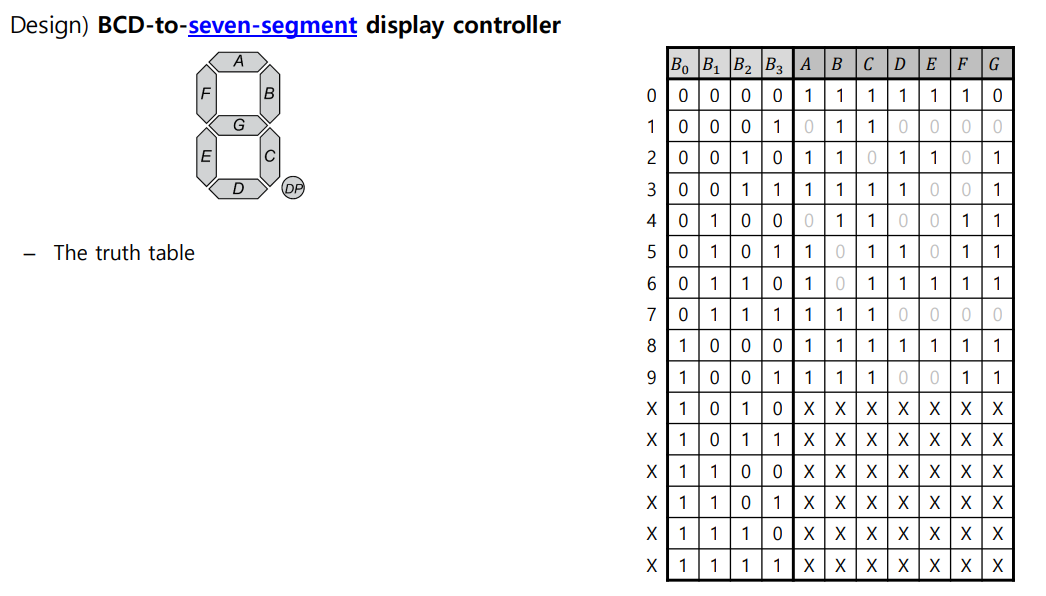

숫자 표기 K-map 연습

- K맵으로 디자인하기

Uploaded by N2T

728x90

'CSE > 디지털 논리' 카테고리의 다른 글

| 9강 Sequential Logic Circuits : 메모리 소자.(Flip-flop과 latch들) (0) | 2023.05.24 |

|---|---|

| 7강 Combinatorial Logic Circuits 더 많은 예제 (0) | 2023.05.24 |

| 5강 Boolean Algebra (0) | 2023.05.24 |

| [디지털 논리 4강] 논리 게이트, 트렌지스터 전압 파형 및 타이밍 다이어그램 (1) | 2023.03.30 |

| [디지털 논리 3강] 문자 인코딩 방식(ASCII,Unicode,BCD 바이너리 인코딩,Gray Code,Parity Bit) (0) | 2023.03.26 |