728x90

복습

Half adder

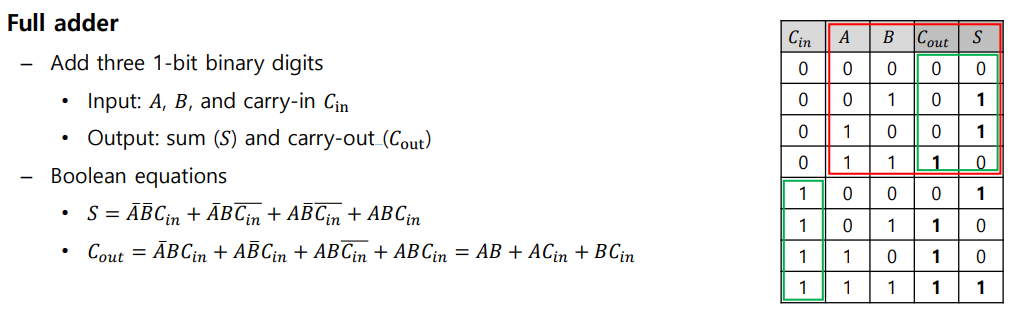

Full adder

Adder

2개의 half adder를 사용하는 Full adder

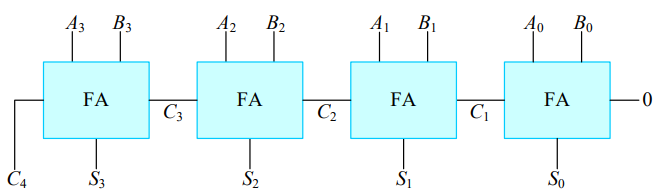

Ripple-carry adder

- 리플캐리 에더는 n비트 바이너리 숫자를 더할 수 있다.

- n개의 full adder의 carry-out bit 는 다음 계산기의 carry-in bit가 된다.

- Parallel adder (병렬 계산기)라고 불린다.

빼기 기능이 있는 리플 캐리 계산기

- 뺄셈은 2의 보수를 이용해서 할 수가 있다.

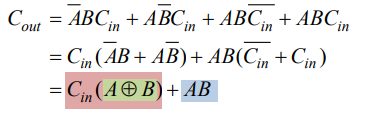

2개의 4비트 계산기를 사용하는 1-nibble BCD adder

BCD와 Binary계산차이

- 바이너리를 BCD로 계산하는 방법 : 합이 9보다 크면 6을 더한다.

- 따라서 BCD 캐리비트를 예측할 필요가 있다.

K-map을 이용한 캐리비트 계산

계산기 예시

Comparator(비교기)

- 주어진 수가 큰지 작은지 같은지에 대해서 비교하는 논리회로이다.

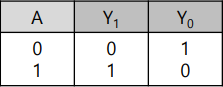

1-bit comparator

2-bit comparator

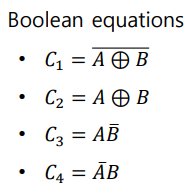

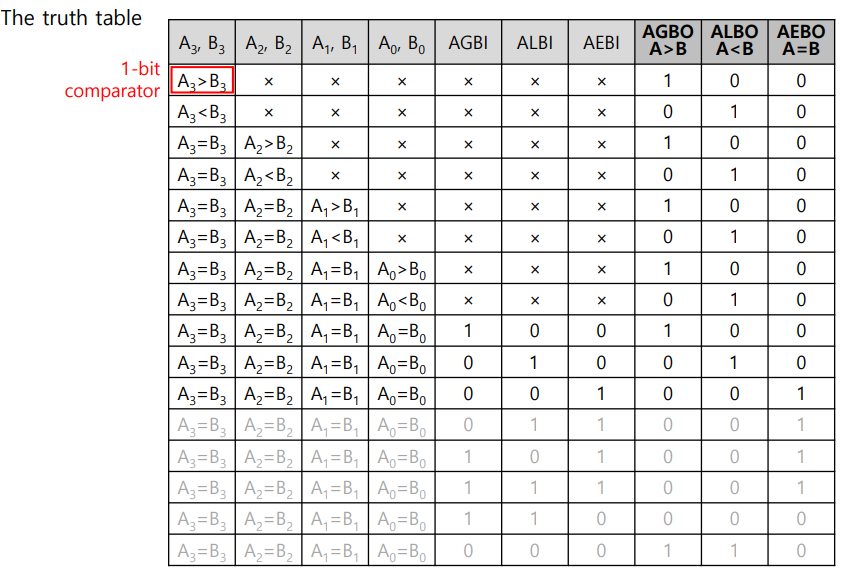

4-bit comparator

- 입력

- 𝐴 (4-bit), 𝐵 (4-bit)

- AGBI (𝐴 > 𝐵), ALBI (𝐴 < 𝐵), AEBI (𝐴 = 𝐵)

- Note) AGBI: A의 입력이 B보다 크다.

- Note) 주로 확장에 사용된다. (~ carry-in in a full adder).

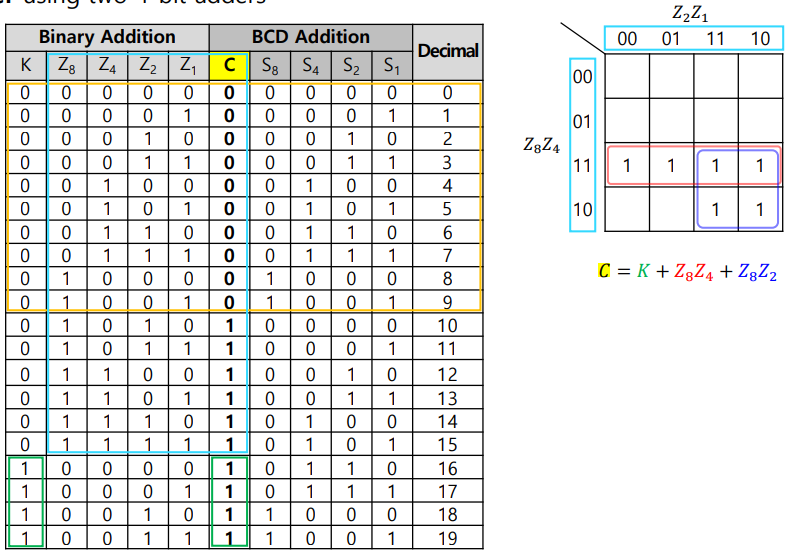

8-bit comparator

4비트 비교기 2개를 사용한다.

Decoder

질문 : 모든 디코더는 다 1 hot출력인가.

- n비트 입력을 최대 2^n개의 고유 출력으로 변환하는 논리 회로

- 예시 : 7세그먼트 display-controller : 4비트 바이너리 입력 → 10개의 출력

- 예시 : 1-of-n 디코더 : n비트 바이너리 입력 → 2^n개 one -hot출력

- one hot 방식 : 1개 빼고 다 0으로 나오는 방식 (머신러닝에서 많이 사용)

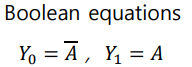

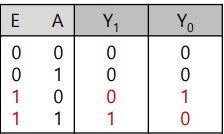

1-to-2 decoder (a.k.a. 1-of-1 decoder)

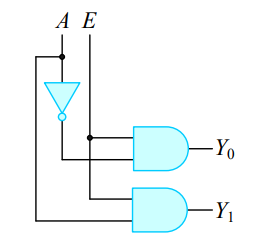

1-to-2 decoder with the enable signal

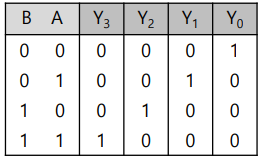

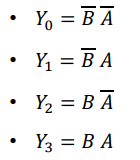

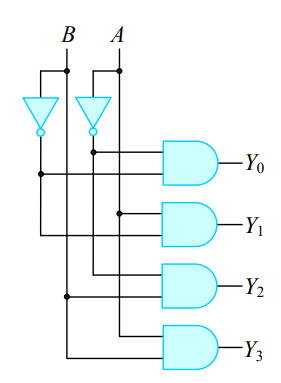

2-to-4 decoder (a.k.a. 1-of-2 decoder)

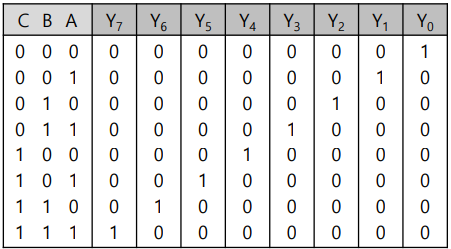

3-to-8 decoder (a.k.a. 1-of-3 decoder)

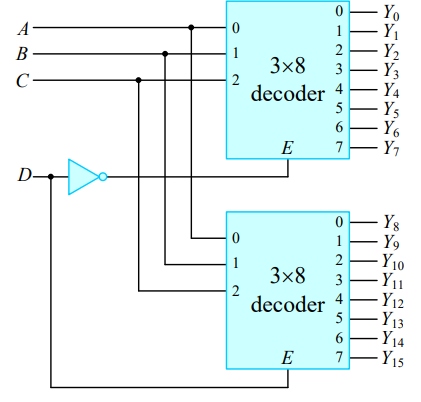

4-to-16 decoder

1-of-n decoder의 특징

- 1-of-n 디코더는 n개의 변수의 SOP식을 구현할 수 있다.

예시 3-to-8 decoder (a.k.a. 1-of-3 decoder)

OR게이트를 추가해서 뭐든지 확장 할 수 있다.

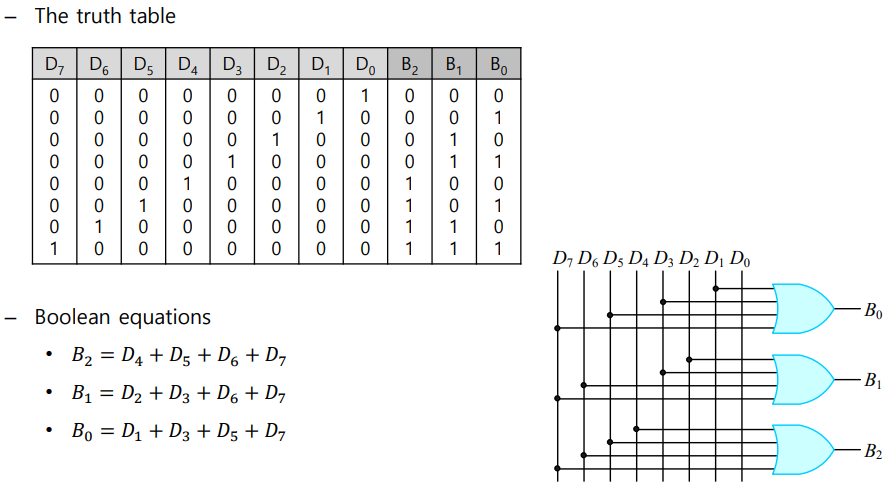

Encoder

- 1 hot을 binary number로 변환시키는 장치

- An inverse of an 1-of-n decoder

2-to-1 encoder

4-to-2 encoder

8-to-3 encoder

Multiplexer and Demultiplexer

- Multiplexer 줄여서 mux (데이터 선택기)은 여러 입력 신호 중에서 단일 출력을 선택하는 장치이다.

- 신호는 디지털 또는 아날로그이다.

- 모니터는 HDML입력 또는 RGB 또는 Display port 중에서 입력 신호를 선택한다.

- 반대로 Demultiplexer(dmux)는 하나의 입력을 여러개의 출력 중에 하나의 방향을 선택하는 장치이다.

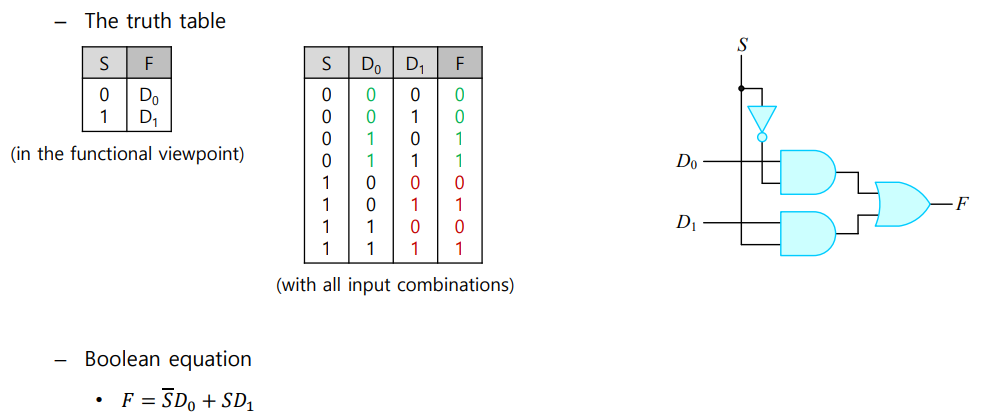

Multiplexer

2-to-1 multiplexer

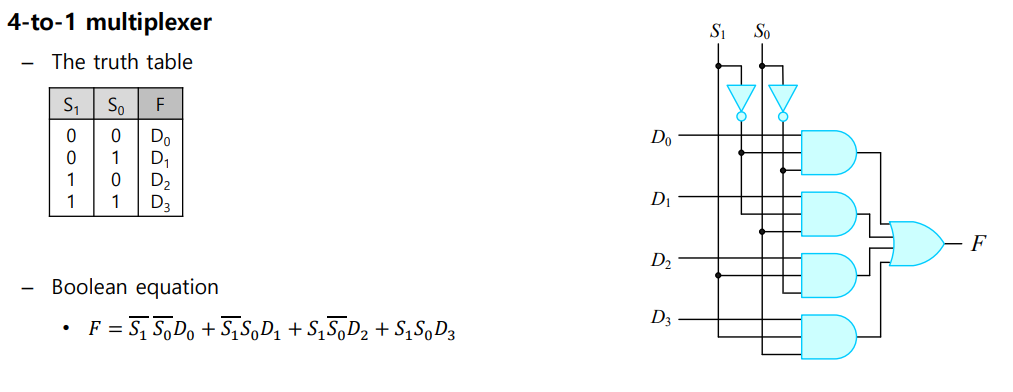

4-to-1 multiplexe

8-to-1 multiplexer

16-to-1 multiplexer using five 4-to-1 multiplexers

멀티플렉서를 사용한 조합 논리 설계

- 입력 : 벌티 플렉서의 Selection bits

- 논리 구현 : 0 또는 1로 주어진 데이터 비트

Demultiplexer

- 디멀티 플렉스는 활성화 신호(enable signal)가 있는 디코더와 동일하게 동작한다.

- Input data ~ Enable signal

- Selection bits ~ Input data

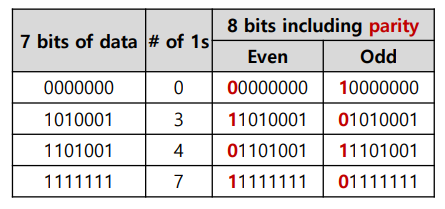

Review) Parity Bit

- 가장 간단한 형태의 오류감지 코드

- 패러티 비트는 1의 총 갯수가 짝수인지 홀수인지 검사한다.

- 짝수 패리티 비트 : 1의 갯수 (패리티 비트 포함) 짝수이면 정답이다.

- 홀수 패리티 비트 : 1의 갯수 (패리티 비트 포함) 홀수이면 정답이다.

제한 사항

- 패리티 비트는 1비트 오류만 감지 가능

- 패리티는 1비트 이상 오류는 감지 부락.

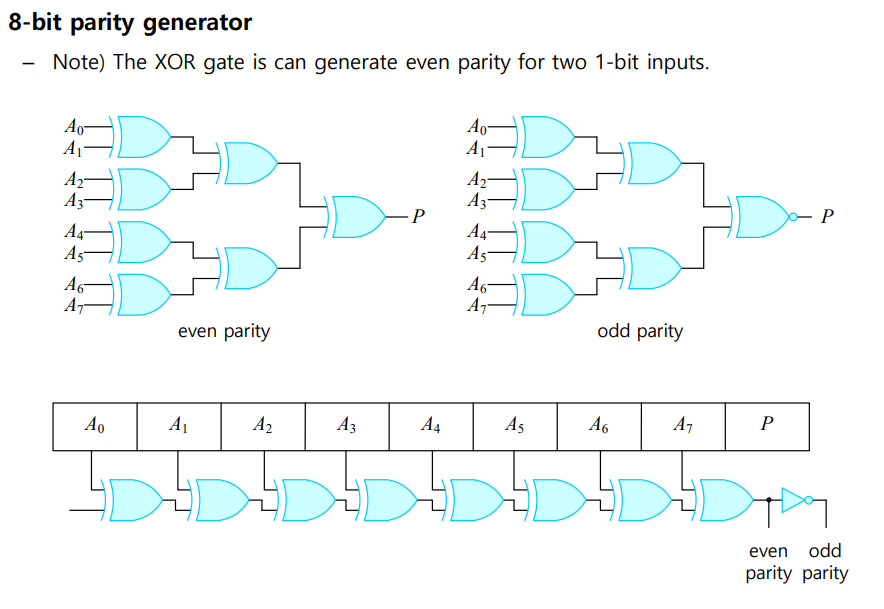

8bit parity generator

- XOR게이트는 2개의 1비트 입력에 대해서 짝수 패리티를 생성할 수 있다.

Uploaded by N2T

728x90

'CSE > 디지털 논리' 카테고리의 다른 글

| 10강 Sequential Logic Circuits2 Design Process (Finite-state Machine(FSM) State transition table,Excitation table, 동기 카운터) (0) | 2023.05.24 |

|---|---|

| 9강 Sequential Logic Circuits : 메모리 소자.(Flip-flop과 latch들) (0) | 2023.05.24 |

| 6강 Combinatorial Logic Circuits 01 (0) | 2023.05.24 |

| 5강 Boolean Algebra (0) | 2023.05.24 |

| [디지털 논리 4강] 논리 게이트, 트렌지스터 전압 파형 및 타이밍 다이어그램 (1) | 2023.03.30 |