728x90

- 어떻게 Sequential Logic Circuits을 만들지 다뤄보겠다.

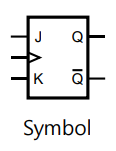

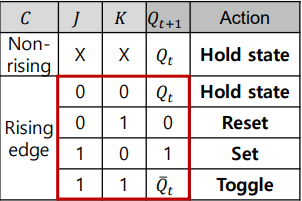

JK Filp flop 복습

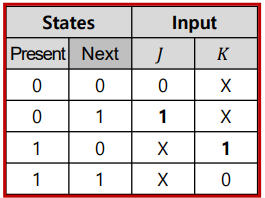

여가표 (Excitation table)

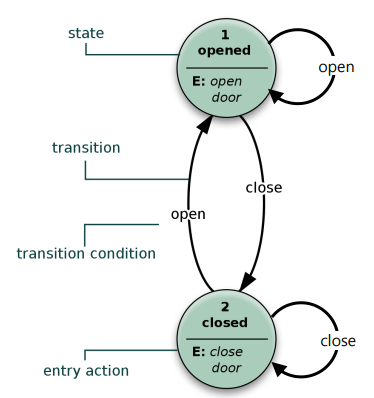

- Finite-state Machine : 우리가 Sequential Logic Circuits을 쓸 때 state를 가지고 있는데 그 state를 표현할지에 대해서 어떻게 표현할 지 보여주기 때문에

- Design Process of Sequential Logic Circuits

Finite-state Machine(FSM)

- 프로그래밍 할 때도 많이 사용된다.

- 현재 내가 짜고싶은 알고리즘을 표현 할 수 있다.

- 한정된 상태를 가진 계산 모델이다.

- state가 변화하는 걸 state transition 이라고 부른다.

- 보통 FSM은 state transition table or a state diagram 2가지로 표현이 된다.

State transition table (~ truth table)

- 별명 : Characteristic table

State diagram (~ directed graph)

- 상태가 노드이고

- 상태의 변화가 선이다. 방향

Design process

1. Define a state transition table or a state diagram

- 요구사항을 가지고 state transition table 이나 다이어그램을 만들면

- state 가 몇개인지 알수가 있다.

- 또한 불 필요한 것들을 줄일 수 있다.

2. Select flip-flops and derive their excitation table.

- 내가 사용할 플립플랍을 결정한다.

- 그 플립플랍의 excitation table을 그린다.

- 보통 상태가 5개면 3개의 플립플롭이 필요하다.

- 보통 카운터 타입을 만들 때는 jk플립플롭이 선호된다.

- 보통 레지스터 같이 저장하는 타입을 D플립 플롭이 선호된다.

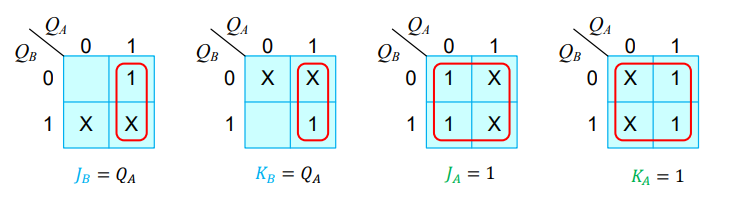

3. Design flip-flop input signals using the K-map.

- excitation table을 이용해서 K-map을 그려준다.

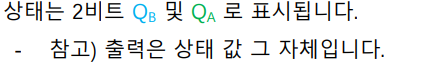

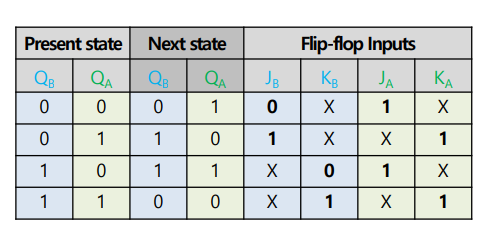

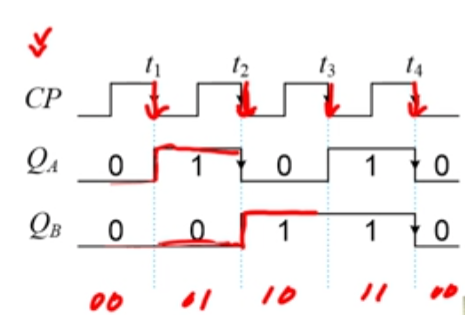

2비트 동기 카운터 예시

- 카운터는 로직 서킷인데 상태가 숫자로 되어있고 특정한 이벤트의 횟수를 저장하는 논리 회로이다.

- 보통 특정한 이벤트를 클럭 시그널의 라이징 엣지를 많이 이야기 한다.

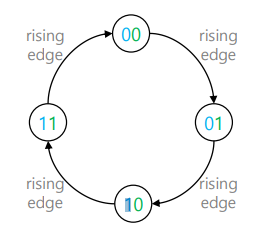

State diagram

- 상태 자체가 output이 된다.

Excitation table

입력 신호 설계

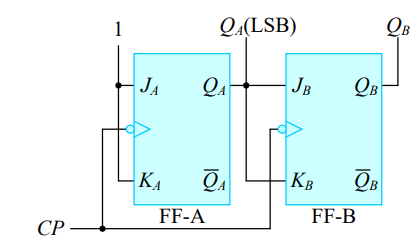

구현

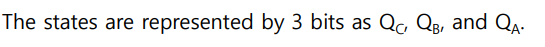

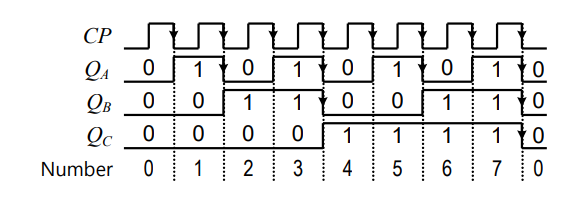

3비트 동기 카운터 예시

State diagram

- 상태 : 8개

Excitation table

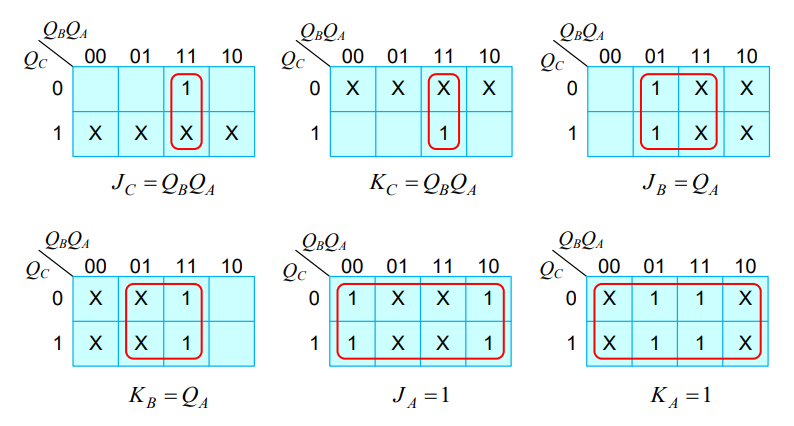

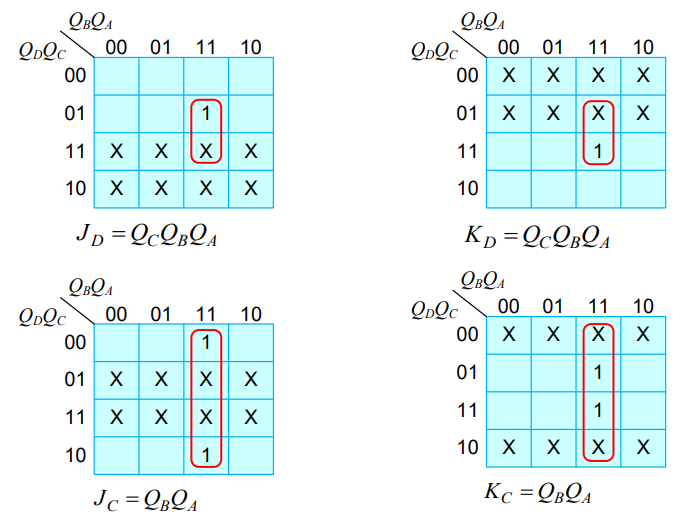

Input signal design(꼭 해보기!!)

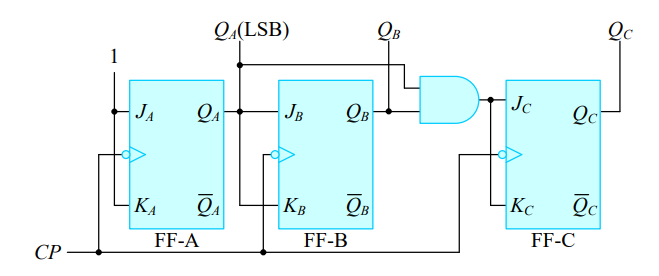

Implementation

재밌는 부분은 2비트 동기 카운터가 있다.

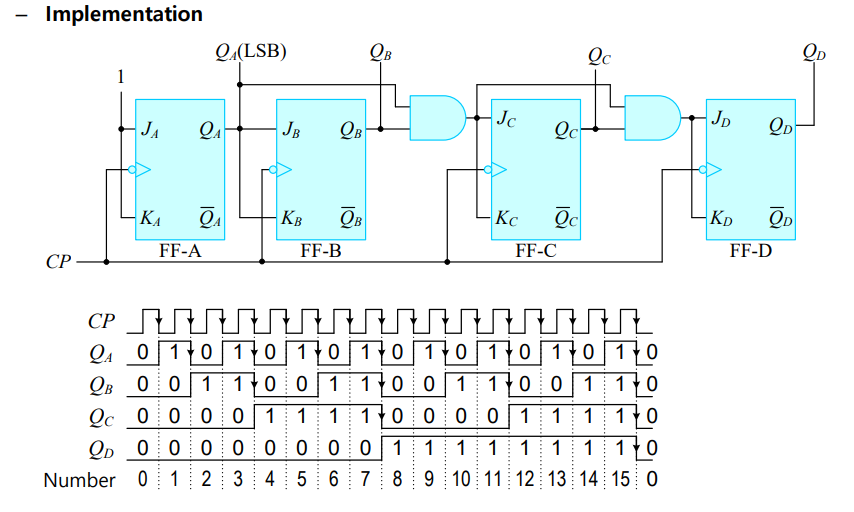

4비트 동기 카운터 예시

빈칸 채울 수 있어야 합니다.

k map 해보기

결과 도출 식

구현

- 중첩 되는 구조가 인상적이다.

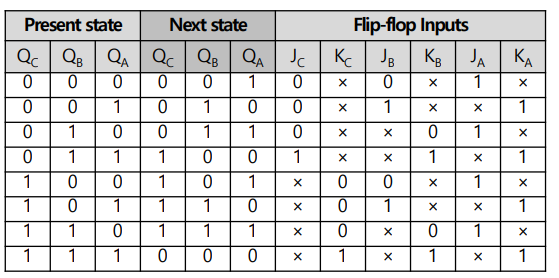

왜 jk flip-flops는 쉽게 카운터를 구현 할 수 있을까?

카운터의 비트 변환을 보면 jk 플립 플롭이 쉬워서

D-flip-flop 사용하는 2비트 카운터 예시

- 이런식으로 AND되서 사라지는 것도 없이 복잡해지기만 한다.

Uploaded by N2T

728x90