728x90

지난 시간에는 동기모드에 대해 배웠다.

이번시간은 비동기모드 카운터와 레지스터에 대해 배운다.

동기 카운터는 같은 클럭 신호를 받았었다.

복습 : 동기 카운터

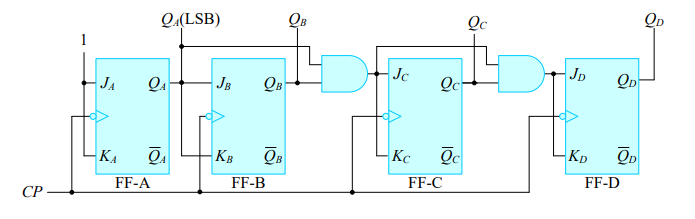

- 4비트 동기 카운터는 4개의 j-k flip flop을 이용하면서 and gate 2개를 이용해서 셀 수가 있었다.

비동기 카운터

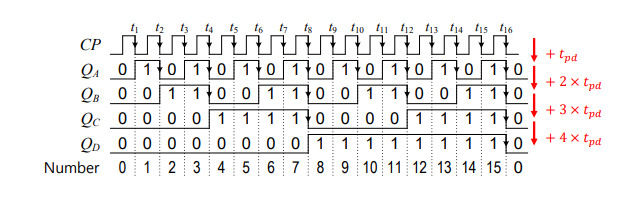

- 비동기 카운터는 플립플롭이 공동 클럭 신호를 사용하지 않는 카운팅 회로이다.

- 비동기 카운터의 클럭 시그널은 이전 출력에서 나오는 JK플립플롭의 결과 값이다.

- 이전에 동기 카운터에서는 가장 앞에 J,K에만 1이 들어갔지만 이제 비동기는 모든 J,K에 1이 들어가게 된다.

- 이말은 쉽게 말해서 모든 JK-Flip-Flop이 토글 모드로 동작한다는 의미이다.

- 이것의 별명은 Ripple counter이다. (이유: 파도처럼 작동하기 떄문에)

- 이슈 : The accumulated propagation delay time(누적전파 지연시간)은 지연상태 전환이 발생해서 잘못된 카운팅이 발생 할 수 있다.

- 비동기 카운터에 대한 timing constraint 계산

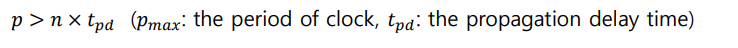

다만 큰 문제가 있다. (약간의 딜레이 계속 증가)

- 𝑝 > 𝑛 × 𝑡𝑝𝑑 (𝑝𝑚𝑎𝑥: the period of clock(시계 주기), 𝑡𝑝𝑑: the propagation delay time(전파 지연시간)) 즉 이 조건을 만족해야만 한다.

- 이 식 매우 중요!!

- 최소 시계 주기 > 전파 지연시간 * N

- 최대 주파수 : 1/(80 * 10^-9) = 12.5MHZ

- 그 딜레이가 propagation delay time이라고 부른다.

Q. 비동기 카운터 언제 쓰는지 + 위의 그림은 이상적인 상황이고 실제로는 오른쪽으로 조금씩 밀리는건지.

A. 밀리고 비동기 거의 안 쓴다.

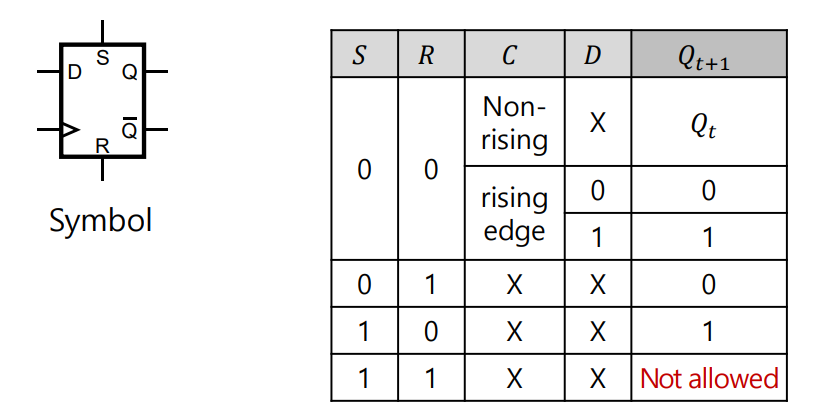

Direct Control Inputs to Flip-flops(복습)

일부 플립플롭은 비동기 입력 신호를 수신하여 상태를 초기화 한다.

- – The direct input signals는 SR래치의 설정(프리셋)및 재설정(클리어)와 유사하다.

- 예시 SR-D-flip-flop

Modulo-m Counter

- Modulo는 나머지라고 생각하면 된다.

- 모듈러 m카운터는 미리 정의된 숫자 m까지 카운트 할 수 있다.

- %(모듈로) 명령은 : 나머지이다.

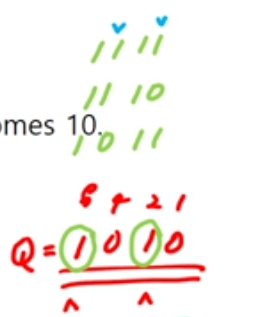

- Modulo-10 asynchronous counter

- (0~9까지 센다.)

- 숫자 10이되면 재설정(지우기 명령)이 활성화 된다.

- 10이 되려하면 즉시 리셋된다.

- 10 : [1010] 4개의 비트를 AND게이트로 연결해서 보면 되는데..

- 0일 때 clear해주기 때문에 Not을 붙혀서 들어가는 것을 볼 수가 있다.

- 그 이유는 1X1X의 경우는 전부 다 초기화 해주면 되기 때문이다.!

- 즉 10이상은 다 초기화가 되기 때문!

4-digit asynchronous decimal counter

- BCD counter라고 부른다.

- 0000에서 9999까지 셀 수 있다.

- MSB가 당음 카운터의 클럭 신호에 연결된 4개의 BCD카운터 체인이다.

- 9에서 10으로 갈 떄 falling edge가 발생하기 때문에!

Preset Counter

- 이건 카운터가 주어진 숫자로부터 시작된다. (몇부터 숫자를 셀 수 있는 것..!)

- Set을 Preset이라고 부르기도 하고, reset 을 CLR이라고 부르기도 한다.

- Load = 0 일때 그냥 비동기 카운터이다.

레지스터 공부 전 복습

Tri-state Buffer Gate복습

- Z는 undefined 로지심은 U라고 씀

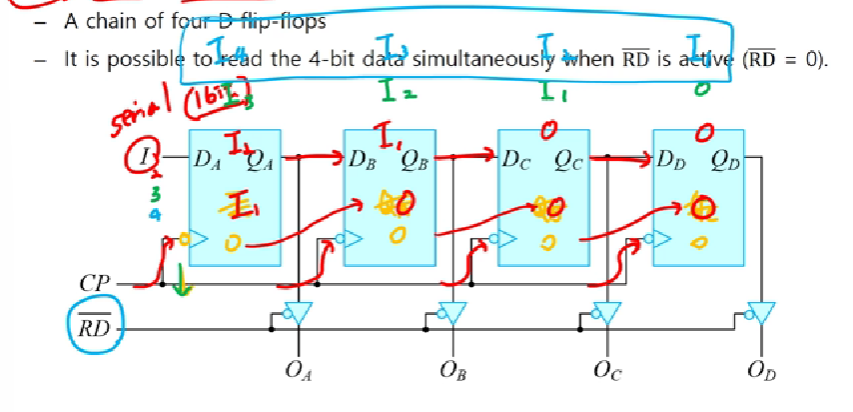

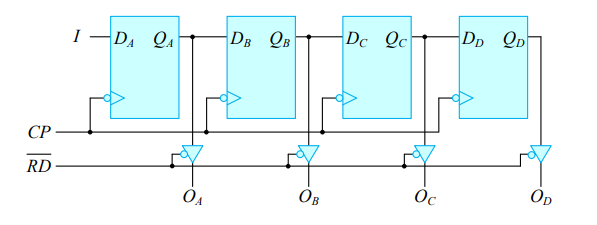

Serial-to-Parallel Register

직렬 병렬 레지스터

- 레지스터는 특수 하드웨어 관련 기능을 갖춘 멀티비트 메모리 요소(일반적으로 플립플롭으로 구성)입니다.

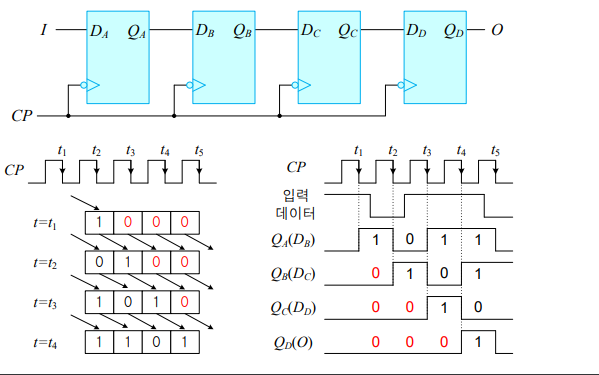

- D플립플롭을 사용하는 4비트 직렬-병렬 레지스터이다.

- Input이 들어올 때 순서대로 쭉 들어온다.(0101이런식)

4-bit serial-to-parallel register using D flip-flops

- 클럭이 쭉 들어오고, 입력이 Serial 1비트로 들어온다. (Serial은 1bit라고 생각하면 된다.)

- 이 그림에서는 Falling edge 이다.

- 입력이 1비트 시리얼로 들어온 것을 출력을 4비트로 바꿔준 것이다.

복습 2 Multiplexer

- 값을 선택해 주는 것이다.

- 입력이 여러개 이고 출력이 하나 일 때 입력중에 어떤 입력을 내보낼 지를 정해주는 것이다.

4-bit parallel-to-serial register using D flip-flops

- 아까와 반대입니다.

- 입력을 선택할 수 있게 해주는 MUX 멀티 플렉서(3개), D-flip -flop(4개)가 필요하다.

- 클럭이 falling edge일 떄 값이 들어오게 되는데..!

- LOAD와 SHIFT가 있는데

- LOAD가 0일 때 : (LOAD하라는 말) : 그럴 떈 IA,IB, IC,ID 이렇게 기억이 된다.

- 그 다음에 SH (Load = 1) : shift 가 동작하고 더이상 IA,IB,IC,ID가 선택되지 않는다.

- 그러면 하나씩 뒤로 튀어나오게 된다.

- 클럭이 falling 될때마다 ID, IC, IB, IA 한비트씩 출력이 된다.

Serial-to-Parallel/Parallel-to-Serial Register 의 활용

- 사용처 Serial data transfers

- USB는 Univarsal serial Bus

- 1비트 여러개를 모아서 1바이트를 만들어 준다.

- 이때 필요한게 Serial-to-Parallel레지스터를 사용하는 것이다. (바이트 단위로 가져올 수 있게 됨)

- 컴퓨터의 데이터를 USB에 저장할 때는 Parallel-to-Serial Register 를 사용합니다.

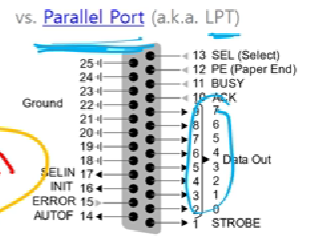

- Serial 데이터를 다시 parallel port 로 보내는 것도 있다.

- USB와 SATA가 나오기 전에 Parallel 을 사용을 많이 했다.

- 왜 시리얼이 더 빠를까?

- 이상하다..! 분명히 parralel이 더 빠른게 정상인데 serial이 더 빠른게 이상하다.

- 고속 전송을 위해 parrallel 보다 Seial이 더 빨랐다.

- 여러 데이터 처리에는 parallel 이 8배는 빠르다.

- 사실 보내는 건 당연히 parallel이 더 빠른데.. 동기화가 문제때문에 더 속도가 느려지는 것이다.

- 시리얼이 더 많이 사용된다.

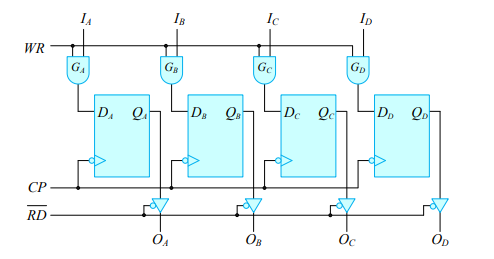

4-bit parallel-to-parallel register using D flip-flop

- 별 기능이 없는 레지스터이다.

- 4개의 D-flip flop로 구성되어 있다.

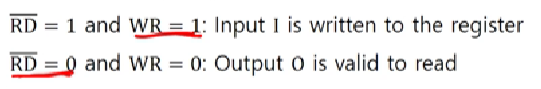

- 입력을 동시에 받아 드릴 수 있도록 하는 WR(Write signal)이 있고

- 준비된 output을 한번에 Ready 시키는 Read 시그널이 있다.

- Write 하고 싶을 때 WR , 읽고 싶을 때 RD

- 사용자 관점에서 Read는 Jk flip-flop의 데이터를 읽는 것 Write는 JK flip-flop에 입력을 넣는 것 입니다.

- 이런 입력도 가능한데

- (RD = 1. WR= 0) 둘 다 Active하지 않은 첫번째 경우는 data를 reset해주고

- (RD = 0, WR = 1) 둘다 Active한 경우는 결과가 바로 씌워지고, 직전에 있던 Signal이 output을 내고 바꾼것도 output이 나온다. (따라서 이건 잘 사용하지 않는다.)

- 따라서 일반적으로 위의 두가지 방식만 가능하다.

parallel-to-parallel register 사용처

- 별다른 특수기능이 없어서 별로 안 쓰인다.

- 메모리 요소로 많이 사용된다.

- 애플리케이션) SRAM(정적 RAM)의 내부의 메모리 요소

- SRAM은 flip-flip으로 으로 구현되어 있고 (DRAM보다 훨씬 복잡한 구조)

- 크기도 훨씬 크다.

- 다만 SRAM은 flip-flop형태로 되어있어서 속도가 매우 빠르다.

- 따라서 CPU cashe나 HDD buffer, router buffer에서 사용

- DRAM(Dynamic ram) 은 Capacitror로 구현되어있다.

- Capacitor는 간단해서 집적도를 높일 수 있다.

- 집적도가 높아서 고용량으로 들어가고 컴퓨터와 GPU의 일반적인 메모리에서 주로 사용

- SDRAM이란 : 이건 Synchronous DRAM이다.

- 이건 우리가 주로 사용하는 DRAM입니다.

Serial-to-Serial Register

- 매우 간단하게 구현되어 있다.

- I가 O로 바로 나온다.

- falling edge 일 때마다 입력 데이터를 가져온다.

- 즉 Clock이 내려올 때마다 하나씩 내려온다.

- 따라서 순서대로 줄줄 나온다.

- 이건 Shift 시킬 때 많이 사용된다.(Bitwise Shift를 시킬때)

- 우리의 shift연산이 속도가 매우 빠른 이유.

- D플립플롭을 사용하는 4비트 직렬 간 레지스터

- D플립플롭 4개 체인

- 응용프로그램 : 비트 단위 이동

Bi-directional Shift Register

- 양방향 Shift 레지스터

- 0을 주면 left로 shift, 1을 주면 Right로 shift한다.

Uploaded by N2T

728x90

'CSE > 디지털 논리' 카테고리의 다른 글

| 13강 Beyond Digital (아날로그, 양자컴퓨터,HDL등등) (0) | 2023.05.24 |

|---|---|

| 12강 Memory and Storage Devices (RAM, SRAM,ROM,FLASH memory) (0) | 2023.05.24 |

| 10강 Sequential Logic Circuits2 Design Process (Finite-state Machine(FSM) State transition table,Excitation table, 동기 카운터) (0) | 2023.05.24 |

| 9강 Sequential Logic Circuits : 메모리 소자.(Flip-flop과 latch들) (0) | 2023.05.24 |

| 7강 Combinatorial Logic Circuits 더 많은 예제 (0) | 2023.05.24 |